4 از 5.0 با 8 رای

ماژول شبکه ENC28J60 برای پروژه های اینترنت اشیا و میکروکنترلر - ماژول اترنت به SPI

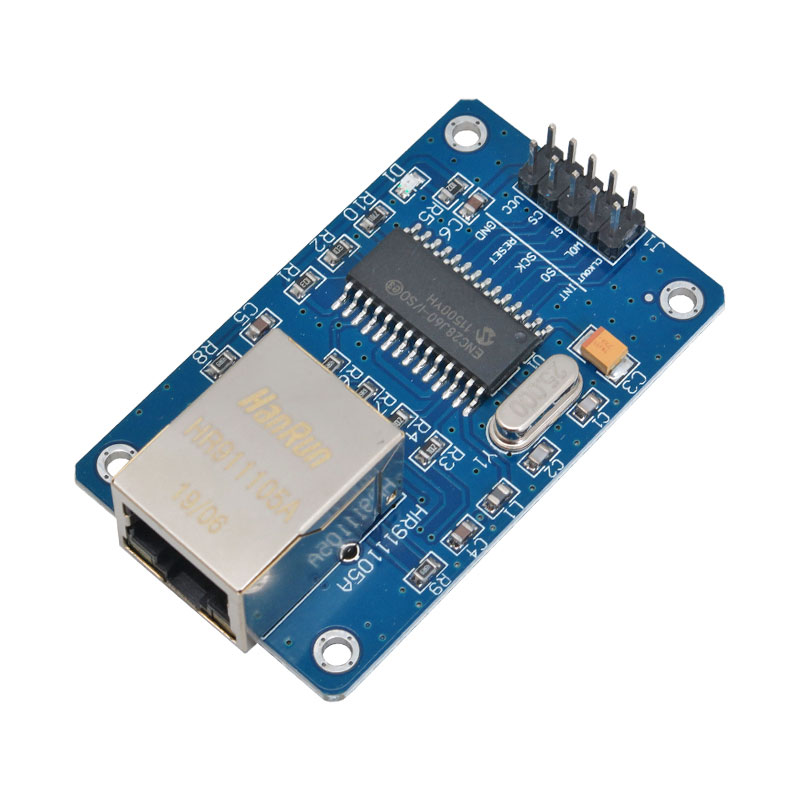

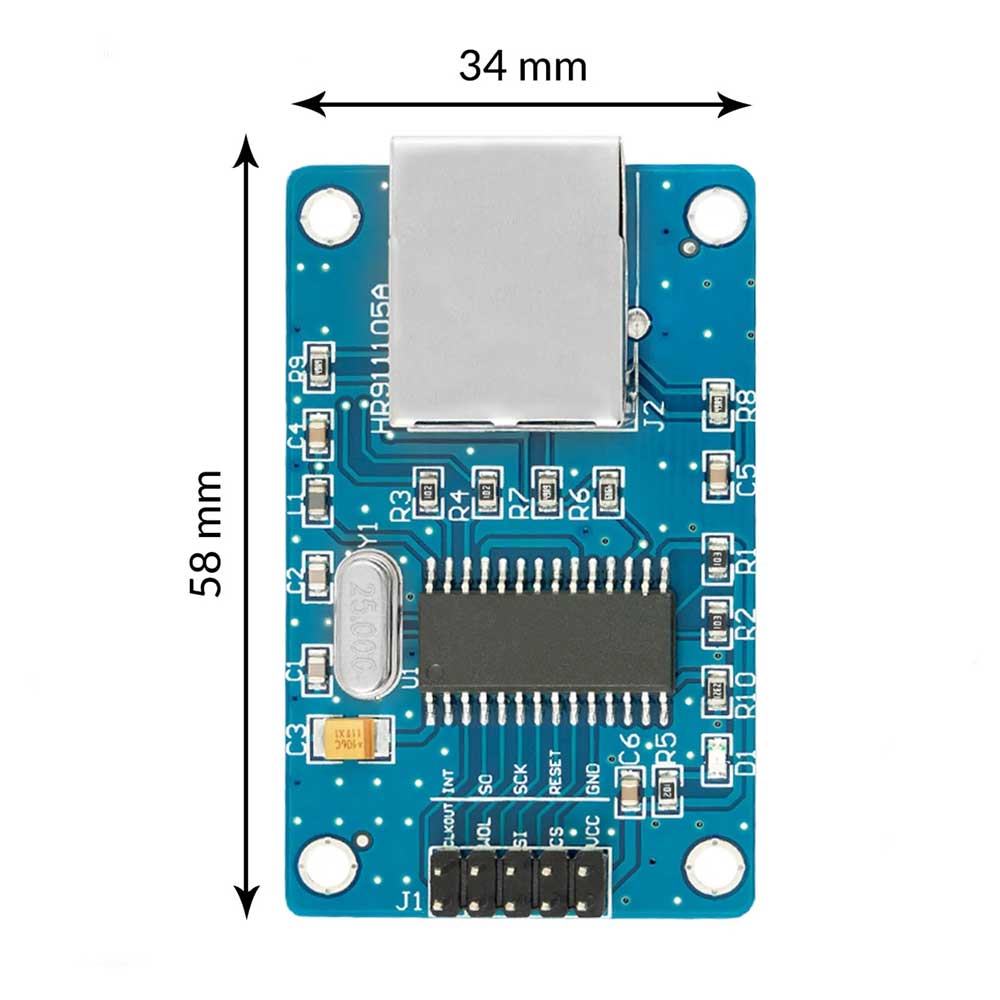

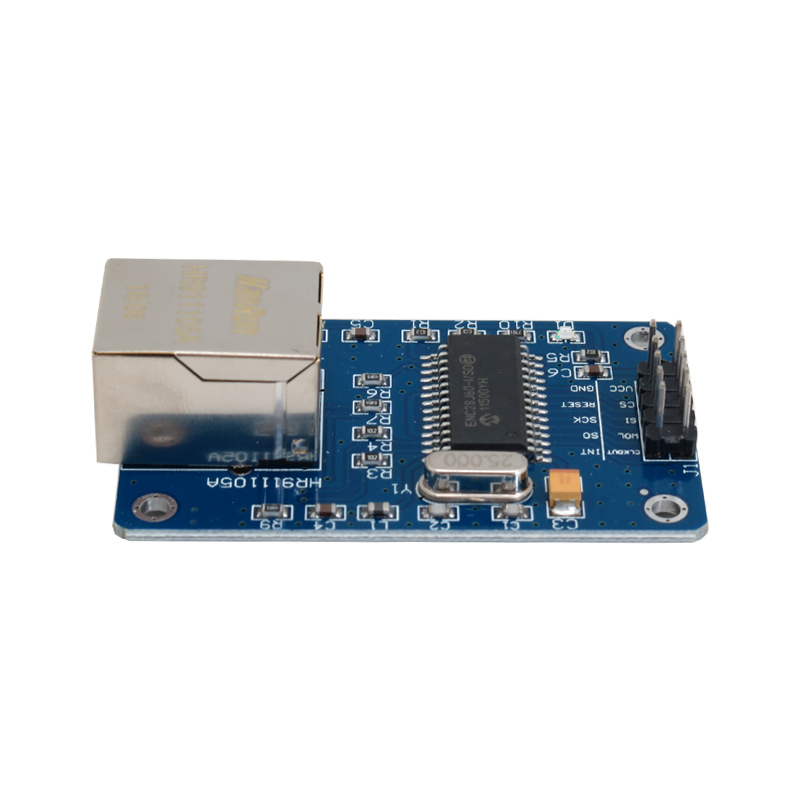

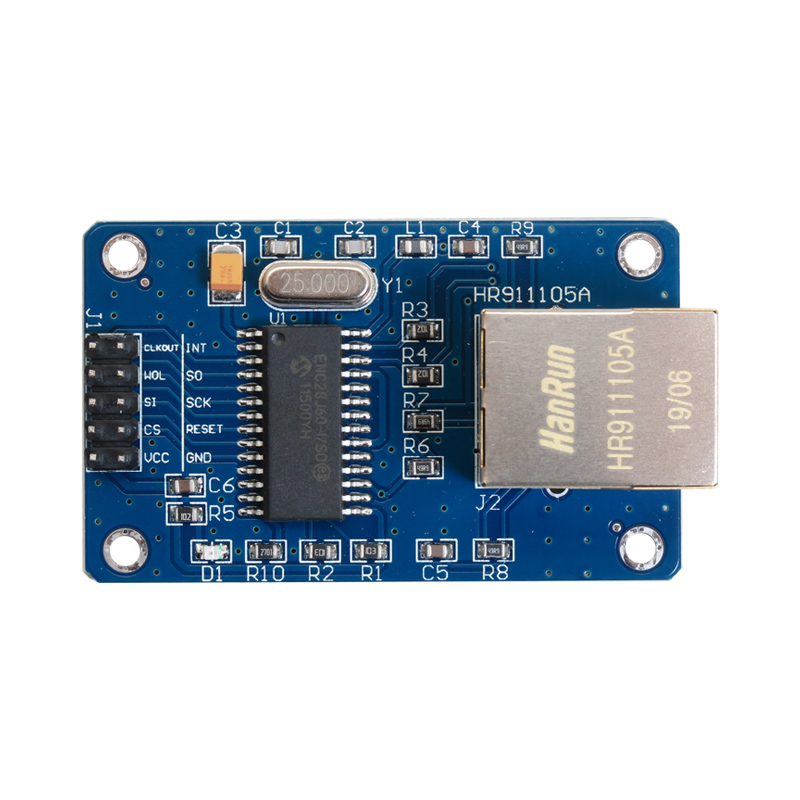

این ماژول برای سنسورها و تجهیزات کنترل از راه دور ، وب سرورهای داخلی و پروژه های IOT مناسب است. واحد MAC کنترل دسترسی به شبکه و پیاده سازی پروتکل های ارتباطی را انجام می دهد و واحد PHY داده های آنالوگ روی کابل اترنت را کدگذاری و رمزگشایی می کند. نشانگرهای LED وضعیت لینک و فعالیت شبکه را نمایش می دهند و ابعاد فیزیکی 56x34 میلی متر نصب آن در مدارها و جعبه های پروژه را ساده می کند.

تغذیه ماژول 3.3 ولت و کریستال 25 مگاهرتز پایداری فرکانسی بالایی ایجاد می کند. پشتیبانی از حالت Half-duplex ، فیلترینگ بسته های ورودی و محاسبه سخت افزاری چکسام بار پردازشی روی میکروکنترلر اصلی را کاهش داده و بازدهی سیستم را افزایش می دهد. مبدل شبکه اترنت به SPI مدل ENC28J60 با خروجی LAN و رابط SPI استاندارد ، عملکرد سریع و دقیق انتقال داده را تضمین می کند و امکان شبکه کردن میکروکنترلرها در فواصل طولانی یا محیط های صنعتی نویزی که وای فای غیرقابل اعتماد است را فراهم می نماید.

ماژول اترنت به SPI برای میکروکنترلر با پشتیبانی از پروتکل های TCP ، UDP ، IP و ARP امکان ایجاد وب سرورها و ارسال داده به سرورهای مرکزی را فراهم می کند. کیفیت ساخت بالا و عملکرد مطمئن ، این محصول را به بهترین ماژول اترنت برای AVR تبدیل کرده است و آن را برای پروژه های صنعتی ، آموزشی و هوشمند کاملاً کاربردی می سازد. طراحی ماژول شبکه LAN با خروجی SPI تجربه ای کامل از اتصال سریع و پایدار به شبکه برای انواع بردهای پردازشی ارائه می دهد و مدیریت داده ها را با دقت بالا امکان پذیر می کند.

کاربرد :

- اتوماسیون خانگی

- برنامه های پزشکی

- سیستم های کنترل و مانیتورینگ

- کنترل سیستم ها و تجهیزات برقی و الکترونیکی از طریق اینترنت

- شبکه کردن مجموعه ای از میکروکنترلرها در فاصله های طولانی

- وب سرورهای اینترنتی

- سیستم های هوشمند

مشخصات :

- تراشه : ENC28J60-I/SO

- استاندارد شبکه : IEEE 802.3

- پروتکل های مورد پشتیبانی : Ethernet , ARP , IP , ICMP , UDP , TCP , PPPoE

- پروتکل ارتباطی : SPI

- رابط فیزیکی شبکه : HR911105A

- فرکانس کریستال : 25 مگاهرتز

- سرعت انتقال داده : 10 مگابیت بر ثانیه

- حالت انتقال داده : نیمه دوطرفه

- نرخ کلاک رابط سریال : تا 20 مگاهرتز

- حافظه بافر داخلی : 8 کیلوبایت

- تعداد پین های نشانگر : 2 عدد برای وضعیت لینک و فعالیت شبکه

- ولتاژ تغذیه : 3.3 ولت تا 5 ولت

- دمای کاری : منفی 40 تا مثبت 85 درجه سانتی گراد

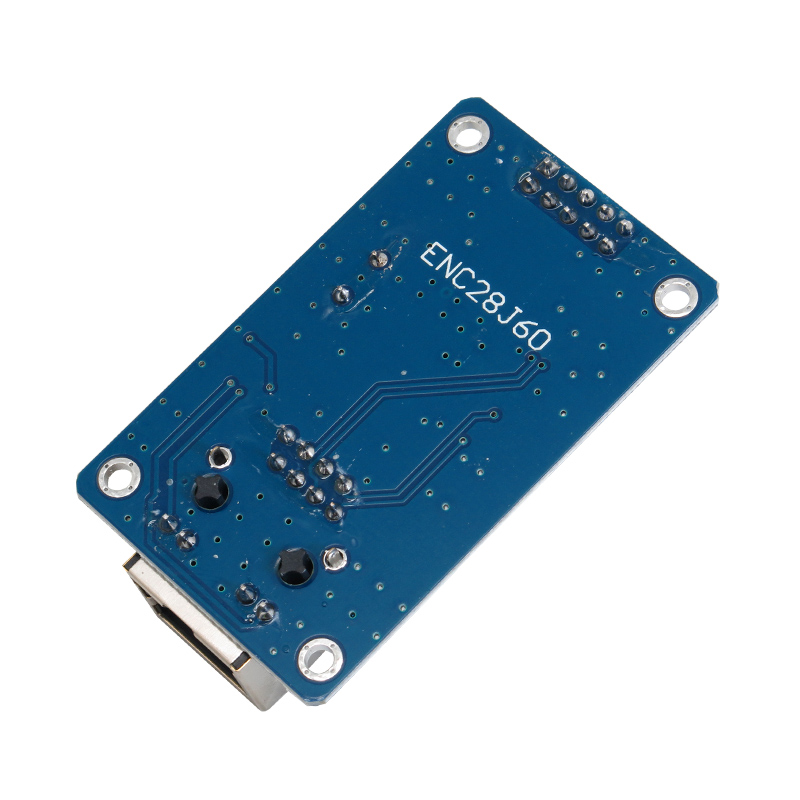

- ابعاد : 56x34 میلی متر

ویژگی ها :

- پشتیبانی از پروتکل های شبکه Ethernet , ARP , IP , ICMP , UDP , TCP , PPPoE

- اتصال آسان به انواع میکروکنترلرها از طریق رابط SPI

- حافظه داخلی 8 کیلوبایت برای مدیریت بسته های داده

- نشانگر LED برای وضعیت لینک و فعالیت شبکه

آموزش راهاندازی ماژول اترنت ENC28J60 با آردوینو:

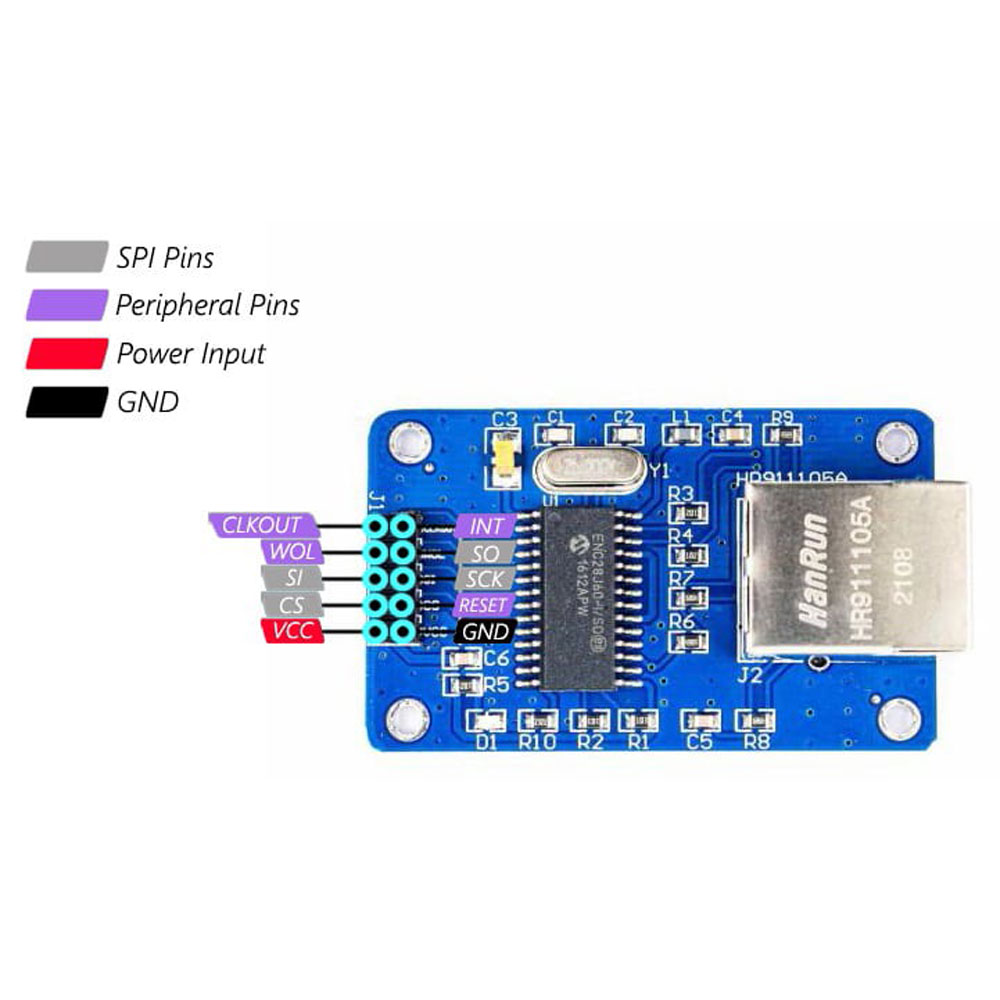

اتصال سخت افزاری صحیح پین های SPI، تغذیه و زمین، و استفاده از کتابخانه های نرم افزاری مانند UIPEthernet یا EtherCard برای مدیریت پروتکل های TCP و UDP . پس از نصب کتابخانه و اتصال ماژول، با برنامه نویسی ساده می توان آدرس IP را تنظیم کرده و داده ها را از سنسورها به سرور مرکزی ارسال یا دریافت کرد.

این ماژول با نمایش وضعیت شبکه از طریق LED و سرعت انتقال مناسب، امکان پیادهسازی پروژه های IOT، وب سرورهای کوچک و سیستم های مانیتورینگ آنلاین را به سادگی فراهم می کند و برای مبتدیان و پروژه های آموزشی نیز مناسب است.

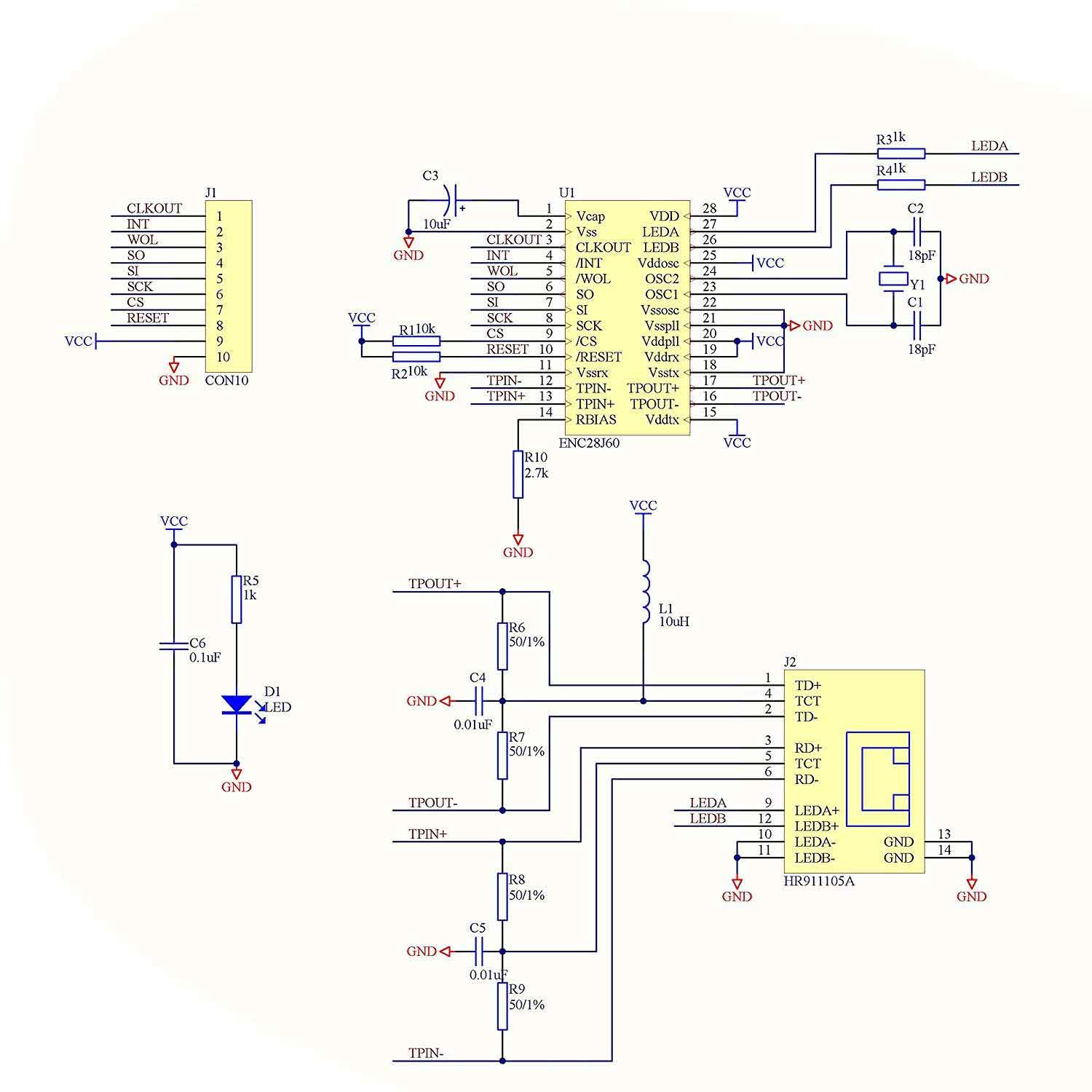

تراشه ENC28J60 شامل هفت بلوک اصلی عملکردی میباشد:

- رابط SPI که به عنوان کانال ارتباطی بین کنترلر میزبان و ENC28J60 عمل میکند.

- رجیسترهای کنترل که برای کنترل و مانیتورینگ ENC28J60 استفاده میشوند.

- بافر رم دو پورت برای بستههای داده دریافتی و ارسالی.

- داوریکننده برای مدیریت دسترسی به بافر رم هنگامی که درخواستها از بلوکهای DMA، ارسال و دریافت انجام میشوند.

- رابط باس که دادهها و فرمان های دریافت شده از طریق رابط SPI را تفسیر میکند.

- بلوک MAC (کنترل دسترسی به رسانه) که منطق MAC مطابق استاندارد IEEE 802.3 را پیادهسازی میکند.

- بلوک PHY (لایه فیزیکی) که داده های آنالوگ موجود در رابط کابل زوج تابیده شده را رمزگذاری و رمزگشایی میکند.

تفاوت ماژول ENC28J60 و W5500 :

عمدتاً در پردازش پروتکل، سرعت و حافظه بافر است. ENC28J60 کنترلر SPI است که پردازش TCP/IP روی میکروکنترلر انجام می شود و سرعت آن 10 مگابیت بر ثانیه است، مناسب پروژه های کوچک و IOT. W5500 با TCP/IP سخت افزاری داخلی و سرعت 10/100 مگابیت بر ثانیه، بار پردازشی را کاهش داده و مدیریت همزمان چند اتصال را ممکن می کند، برای پروژه های صنعتی و وب سرورهای چندکاربره مناسب است. ENC28J60 نیاز به کتابخانه نرم افزاری دارد، در حالی که W5500 راه اندازی آسان تری با کتابخانه سخت افزاری ارائه می دهد.

مستندات:

دانلود دیتاشیت ENC28J60

آموزش آنلاین کردن AVR با ماژول شبکه ENC28J60

نمونه کد آردوینو ماژول اترنت ENC28J60